JIWEIAION仿真平台顺应UCIe新标准

前几天美国朋友发给我CHIPLET新的INTERCONNECT标准以及这几天半导体网上都在讲UCIe(Universal Chiplet Interconnect Express)。细看一下,原来是2014年我在Intel作为IO系统工程师参与设计的在封装上的超短距技术成为了新一代标准。作为第一代UCIe系统开发人员,倍感欣慰。

第一代UCIe的速率在7.2Gbs,主要是连接CPU与封装上的DRAM,32条写通道,32条读通道。当时的设计难点主要在:

- 单端,非常容易受到串扰的影响;

- 信号通道短,直观上的信号完整性不是问题,但是由于信号通道多,供电系统是个大问题;

- 由此产生的电源噪音对信号完整性又是一个大问题,而且电源噪音还跟数据PATTERN强相关。

- 时钟电路中的抖动在这样恶劣环境中的被动放大,程度如何?

- 数据速率很大,系统的非线性问题很严重。

要想解决这些问题,常规的芯片系统设计思路将完全行不通。常规中将IO PHY设计、封装设计、PCB设计分开将变得没有意义。高精度的电磁场仿真对这类接口有用,但不是很重要,所有的模型足够好就可以了。

为了克服以上难点,全新的系统设计思路势在必行。芯片设计、封装设计,以及有可能的PCB板设计必须在同一个设计平台内,需要真正意义上的SI/PI闭环设计。由于非线性问题,系统设计的思路必须围绕时域上的仿真。当时该思路在商业化的平台MATLAB完整实现并且完完全全指导IO设计,并且一次流片成功并且芯片到了量产标准。

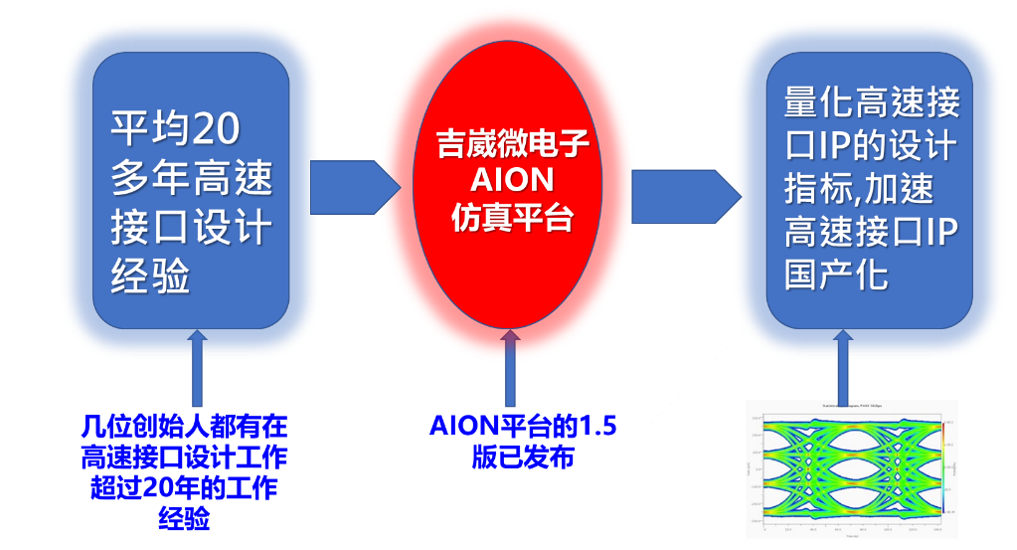

今天昆山吉崴微电子科技有限公司的JIWEIAION EDA工具软件将这种系统设计思路进一步强化,进一步提升IO芯片设计、封装,PCB协同仿真能力,成功发布世界先进的芯片系统仿真平台——JIWEIAION 1.5 版工业软件。其目标就是要解决高速接口的瓶颈问题。JIWEIAION的仿真平台解决问题的思路如下图:

昆山吉崴微电子的愿景就是要成为中国芯片接口系统解决方案的供应商,并且提升整个产业接口设计的能力。

CHIPLET集成电路产业市场的快速膨胀以及其它高速接口的快速发展,昆山吉崴微电子JIWEIAION仿真平台势必会给客户带来全新的仿真理念。